|

|

|

|

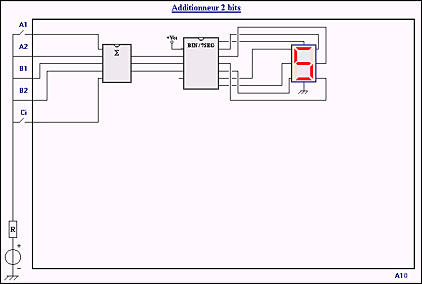

| Ce

circuit permet d’étudier le principe de fonctionnement d’un

circuit intégré, l’additionneur complet 2 bits, qui additionne

2 nombres binaires de 2 bits, A2A1

et B2B1, et éventuellement

un autre bit, Ci (Carry in), pouvant représenter la retenue d’une

addition antérieure.

|

| Le

résultat de l’addition est directement visualisé sur

un afficheur à 7 segments par l’intermédiaire d’un

décodeur BCD / 7 segments. |

|

|

|

|

|

|

|

|

|

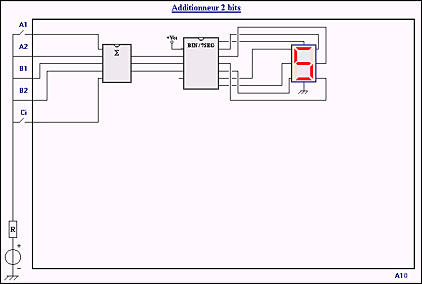

Dans

l’exemple ci-dessus, le nombre binaire A2A1

est égal à 10 (2 en décimal) et le nombre binaire B2B1

est égal à 11 (3 en décimal).

Ci étant égal à 0, le résultat de l’addition

des 2 nombres binaires, A2A1

et B2B1, en décimal

est donc 5 (101 en binaire). |

|

|

|

|

|

|